# Selective p- and n-Doping of Colloidal **PbSe Nanowires To Construct Electronic and Optoelectronic Devices**

Soong Ju Oh,<sup>†,I,⊥</sup> Chawit Uswachoke,<sup>‡,⊥</sup> Tianshuo Zhao,<sup>†</sup> Ji-Hyuk Choi,<sup>†</sup> Benjamin T. Diroll,<sup>§</sup> Christopher B. Murray,<sup>†,§</sup> and Cherie R. Kagan<sup>\*,†,‡,§</sup>

<sup>†</sup>Department of Materials Science and Engineering, <sup>‡</sup>Department of Electrical and Systems Engineering, and <sup>§</sup>Department of Chemistry, University of Pennsylvania, Philadelphia, Pennsylvania 19104, United States and Department of Materials Science and Engineering, Korea University, Seoul 136-713, Republic of Korea.  $\pm$ S.J.O. and C.U. contributed equally to this work.

**ABSTRACT** We report the controlled and selective doping of colloidal PbSe nanowire arrays to define pn junctions for electronic and optoelectronic applications. The nanowires are remotely doped through their surface, p-type by exposure to oxygen and n-type by introducing a stoichiometric imbalance in favor of excess lead. By employing a patternable poly(methyl)methacrylate blocking layer, we define pn junctions in the nanowires along their length. We

demonstrate integrated complementary metal-oxide semiconductor inverters in axially doped nanowires that have gains of 15 and a near full signal swing. We also show that these pn junction PbSe nanowire arrays form fast switching photodiodes with photocurrents that can be optimized in a gated-diode structure. Doping of the colloidal nanowires is compatible with device fabrication on flexible plastic substrates, promising a low-cost, solution-based route to high-performance nanowire devices.

**KEYWORDS:** PbSe · colloidal nanowires · selective doping · pn junction · CMOS inverter · photodiode

olloidal semiconductor nanostructures are of great interest for their unique size-dependent electronic and optical properties and for their solution-based processability that allows these materials to be integrated and their properties to be exploited in devices.<sup>1-3</sup> Among nanostructures, colloidal PbSe nanowires (NWs) are of particular interest because lead chalcogenides have large exciton, electron, and hole Bohr radii, a narrow and widely size tunable band gap, high and similar electron and hole mobility, and anisotropic properties along their one-dimensional axis.<sup>4,5</sup> They are also explored for their potential for multiexciton generation. $^{6-8}$  The unique properties of PbSe nanostructures make them promising semiconductor building blocks in electronic circuitry,<sup>9</sup> multijunction solar cells,<sup>10</sup> near- to mid-infrared photodetectors,<sup>11–13</sup> and hightemperature thermoelectrics.<sup>14,15</sup> Curiously, while bulk PbSe or PbS are the mainstay of near- to mid-infrared photoconductorbased photodetectors, they have not been used to develop photodiodes. The lead

chalcogenides lost in the commercial arena to HgCdTe detectors many years ago because of their high thermal mismatch to underlying substrates, which causes mechanical failure upon thermal cycling,<sup>16</sup> and their high dielectric constant, which resulted in long RC (product of resistance and capacitance) time constants.<sup>17</sup> These two limitations are no longer relevant in today's imaging technology and are overcome in NWs by the lowtemperature and solution-based fabrication of devices. However, there are few reports integrating lead chalcogenide NWs in devices, primarily because of the lack of methods reported to controllably dope these materials.

In this work, we demonstrate processes to selectively p- and n-dope PbSe NW arrays and design pn junctions for electronic and optoelectronic applications. We take advantage of the high surface area of the NWs to remotely dope the NWs by introducing adatoms at their surface. The p-doping is created simply by exposure to oxygen, which introduces acceptors with low ionization

\* Address correspondence to kagan@seas.upenn.edu.

Received for review May 6, 2015 and accepted June 12, 2015.

Published online June 12, 2015 10.1021/acsnano.5b02734

© 2015 American Chemical Society

VOL.9 • NO.7 • 7536-7544 • 2015

14

energy, as we have shown previously.<sup>18,19</sup> The n-doping is realized by applying vacuum- and solutionbased methods to produce an excess of lead, which we demonstrated dopes analogous zero-dimensional nanocrystal films<sup>9,20,21</sup> and here show that the stoichiometric imbalance is effective at creating donors in PbSe NWs.

Employing a poly(methyl methacrylate) (PMMA) blocking layer in our process, we selectively p- and n-dope the NWs to define pn junctions along their lengths. We create axial p- and n-type field-effect transistors (FETs) as building blocks to demonstrate integrated colloidal PbSe NW array complementary metal-oxide semiconductor (CMOS) inverters. The NW CMOS inverters show gains of 15 for signal amplification and inversion of logic output at low and high input voltages for signal switching. We also define pn junctions in NW arrays to create photodiodes that switch >1000 faster than NW array photoconductors. By integrating the NW array pn junctions in a gateddiode structure, we control the carrier statistics and the dimensions of the depletion region to enhance charge carrier collection. To the best of our knowledge, this is the first report demonstrating colloidal NW-integrated electronic circuits and also the first example of colloidal pn junction NW optoelectronic devices. We show that our selective doping processes for PbSe NW arrays are compatible with device fabrication on flexible plastics.

### **RESULTS AND DISCUSSION**

We synthesize colloidal PbSe NWs that are 10 nm in diameter and >10  $\mu$ m in length.<sup>22</sup> Hexadecyl-graftpolyvinylpyrrolidone (HD-PVP, 1%) is added to stabilize the NWs in octane. PbSe NW array FETs are fabricated as a platform to investigate NW doping. Heavily n-doped Si wafers with 250 nm of thermally grown SiO<sub>2</sub> are used as substrates and serve as a back gate and a part of the gate dielectric layer of the FET, respectively. Al<sub>2</sub>O<sub>3</sub> (20 nm) is deposited by atomic layer deposition to complete the gate dielectric stack and to reduce the dielectric-semiconductor interface trap density and device hysteresis. Source and drain electrodes are patterned via standard photolithography and thermal evaporation of Au to define FET channels with a length of 20  $\mu$ m and a width of 300  $\mu$ m. Substrates are immersed in a solution of (3-mercaptopropyl)trimethoxysilane (MPTS) (5 vol % in toluene) for 24 h to enhance the NW-substrate adhesion and further reduce the device hysteresis.<sup>23</sup> PbSe NWs are electrophoretically aligned across the channel of the FET by depositing a drop of the NW dispersion in octane onto the gate dielectric surface while applying an electric field of 10<sup>4</sup>-10<sup>5</sup> V/cm across the junction.<sup>24</sup> The octane is allowed to evaporate, and then the samples are washed with methanol and chloroform to remove impurities, excess organic compounds, and polymer. The PbSe NW FETs are immersed in a 10 mM solution of NH<sub>4</sub>SCN<sup>25-28</sup> in methanol to remove the

OH ET AL.

bulky insulating tetradecylphosphonic acid and oleic acid ligands used in synthesis and displace the HD-PVP used to aid dispersion and replace them with the compact thiocyanate ligand (Supporting Information Figure S1A). Ligand exchange reduces the device contact resistance and enhances the conductivity.<sup>19</sup> TEM images (Supporting Information Figure S1B–D) confirm that ligand exchange with thiocyanate does not change the PbSe NW morphology, in agreement with a previous report,<sup>29</sup> and does not lead to NW agglomeration.

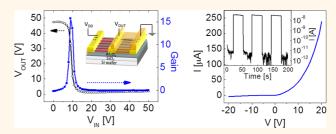

Figure 1A depicts an aligned PbSe NW array FET. As-prepared and thiocyanate-exchanged PbSe NW FETs show ambipolar characteristics seen by v-shaped transfer characteristics (Figure 1B, black curve) and by an increase in current at low  $V_{\rm G}$  and high  $V_{\rm DS}$  in the output characteristics (Figure 1C), as electrons (holes) are injected at the drain electrode in the hole (electron) accumulation regimes.<sup>29</sup> Ambipolar behavior in PbSe NW FETs is consistent with the similar electron and hole effective masses and the mirror-like electronic structure of PbSe, as previously reported.<sup>5</sup>

Figure 1A also portrays the general scheme we use to investigate the doping process and create p-type or n-type devices. For this purpose, we introduce surface adatoms to remotely dope the NWs. We expose the NW arrays to controlled doses of oxygen gas in a UV-ozone chamber to produce p-doping. Foreign oxygen atoms are known to create acceptor states in lead chalcogenide nanostructures, thin films, and bulk crystals.<sup>18,19,30-32</sup> To n-dope the PbSe NWs, we introduce excess lead ions or atoms to generate a stoichiometric imbalance through solution-based PbCl<sub>2</sub> treatment in oleylamine or through thermal evaporation of elemental lead, respectively. Lead enrichment and therefore chalcogen vacancies are known to create donor states in lead chalcogenides<sup>30</sup> and, as we have shown, in lead chalcogenide nanocrystal thin films.9,20,21

The transfer characteristics in Figure 1B show that oxygen and lead adatoms successfully dope the PbSe NWs, transforming the ambipolar, thiocyanateexchanged FETs into p-type and n-type FETs, respectively. Excess oxygen (lead) enhances the hole (electron) current, reduces the electron (hole) current, and shifts the threshold voltage ( $V_{TH}$ ) to positive (negative) voltages, reflecting a shift in the Fermi level toward the valence (conduction) band.<sup>20</sup> The hysteresis in the transistor characteristics is dominated by trap states at the semiconductor NW-gate dielectric interface.<sup>23</sup> Optimization of the gate dielectric surface modification and pn junction fabrication process may reduce the device hysteresis and increase the noise margin for electronic circuitry. The output characteristics of the oxygen p-doped and lead n-doped FETs are shown in the respective hole and electron accumulation regimes in Figure 1D. Comparison between the

RTICLE

JAI

www.acsnano.org

Figure 1. (A) Schematic of PbSe NW FETs and their p-type and n-type doping through the introduction of surface oxygen and excess lead atoms. (B) Transfer characteristics at  $V_{DS} = \pm 20$  V for PbSe NW FETs before (black) and after oxygen (blue) exposure or lead (red) deposition by thermal evaporation (solid line represents the forward sweep, and dotted line represents the reverse sweep). Output characteristics of (C) undoped PbSe NW FETs and (D) oxygen-doped p-type (left) and lead-doped n-type PbSe NW FETs (right).

output characteristics of ambipolar FETs (Figure 1C) and p-type and n-type FETs (Figure 1D) emphasizes the 50 $\times$  increased hole and electron currents achieved through doping, as the carrier concentrations are increased and the carrier mobilities are increased due to trap state filling discussed below.

We estimate the effective mobilities of the PbSe NW FETs from the transfer characteristics by using the lithographically patterned channel dimensions (i.e., assuming the channel is completely filled with NWs and that it serves as a thin film). We note here that calculating the mobility using the Wunnicke capacitance<sup>33</sup> for each nanowire gives similar values. The actual coverage of the channel is less than 10%, and therefore, the device mobilities underestimate the PbSe NW carrier mobilities by >10×. The saturation regime electron mobility for n-type NW FETs is  $11 \pm 2.5$  cm<sup>2</sup>/Vs, and the hole mobility for p-type NW FETs is  $15 \pm 2 \text{ cm}^2/\text{Vs}$ , both of which are higher than those of ambipolar NW FETs (electron mobility =  $0.8 \pm 0.2 \text{ cm}^2/\text{Vs}$  and hole mobility =  $1.3 \pm 0.3 \text{ cm}^2/\text{Vs}$ ). Similar mobilities are found from the linear regime characteristics, with an electron mobility of 10  $\pm$  1.4 cm<sup>2</sup>/Vs for n-type FETs, a hole mobility of 15  $\pm$  2.2 cm<sup>2</sup>/Vs for p-type FETs, and electron and hole mobilities of 0.7  $\pm$  0.2 and 1.2  $\pm$ 3 cm<sup>2</sup>/Vs for ambipolar FETs, respectively. The increase in mobility upon n- or p-doping is attributed to the filling of trap states introduced by unsatisfied bonding at the NW surface and by the NW-gate dielectric interface.<sup>20,34</sup> After doping, the I<sub>ON</sub>/I<sub>OFF</sub> of the NW FET ratio increases from  $\sim$ 100 to  $\sim$ 1000, as  $I_{\rm ON}$  increases more significantly than the increase in  $I_{OFF}$ . This is consistent with the transport of a greater concentration of carriers with high mobility in the on-state, as traps are filled and carriers occupy higher energy states, in comparison to the carrier transport in the off-state.

The p- and n-doping of the PbSe NW arrays can be controlled by the "dose" of the treatment used to introduce oxygen or excess lead. By increasing the exposure time of the FET in the UV-ozone, the oxygen p-doping increases and the FET behavior is modulated from ambipolar to lightly p-type and eventually to heavily p-type (Supporting Information Figure S2A). By increasing the time that the device is placed in the PbCl<sub>2</sub> solution in oleylamine, a greater number of lead ions are bound to the NW surface and the device becomes more n-doped (Supporting Information Figure S2B,C). In the case of the thermal evaporation method, the more lead deposited, the more n-type the FETs become. If too much lead (>12 Å) is evaporated, the device becomes heavily doped and shows semimetallic, degenerate behavior (Supporting Information Figure S2D).

We estimate the change in electron ( $\Delta n$ ) or hole ( $\Delta p$ ) concentration with the dose of the treatment used to dope the NWs by  $\Delta n$  or  $\Delta p = \Delta V_{TH}C_{ox}/q$ , where  $\Delta V_{TH}$  is

VOL.9 NO.7 7536-7544 2015

IAI

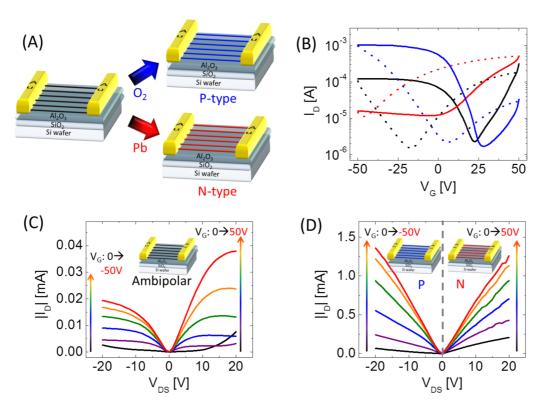

Figure 2. (A) Schematic of the fabrication process and (B) SEM image of an integrated CMOS PbSe NW array inverter created by p-doping through exposure to oxygen and n-doping through thermal evaporation of lead. (C) Voltage transfer characteristics and (D) switching behavior of the inverter in response to a square wave input. Inset in (C) is the circuit diagram of the CMOS inverter.

the shift in the threshold voltage extracted from the transfer characteristics,<sup>35–38</sup>  $C_{ox}$  is the capacitance of the oxide layer (1.33 nF/cm<sup>2</sup>), and *q* is electrical charge. For example, a  $\Delta V_{TH}$  of -10 V is seen in NW FETs by thermal evaporation of 4 Å of lead or by immersion in a PbCl<sub>2</sub> solution at 80 °C for 10 min, resulting in an increase in mobile electron density of  $\sim 7 \times 10^{17}$ /cm<sup>3</sup>. A  $\Delta V_{TH}$  of +10 V is realized by a 1 min exposure of the NWs to oxygen, now increasing the hole density by  $\sim 7 \times 10^{17}$ /cm<sup>3</sup>. These doping levels are similar to those we reported previously for the introduction of excess lead in nanocrystal thin films.<sup>20,21</sup>

Utilizing these doping methods, we fabricate pn junctions in the PbSe NWs of the arrays to build integrated CMOS inverters. For the example of the CMOS inverter, we begin by using electron-beam lithography and thermal evaporation of Au to pattern three electrodes in parallel. We deposit aligned NWs across the device by applying the electric field between the outer pair of electrodes. The distance between the outer pair of electrodes is 20  $\mu$ m, as we used above, and the added middle electrode is 4  $\mu$ m, defining left and right FETs with channel lengths of 8  $\mu$ m. To selectively dope one side of the junction, the other side needs to be protected from doping. We use PMMA as an electron-beamsensitive, patternable blocking layer. We found that while the PMMA is permeable to oxygen and therefore does not serve as a blocking layer toward oxygen,

OH ET AL.

PMMA is a suitable blocking layer for the solutionbased addition or thermal evaporation of excess lead, protecting the PbSe NWs underneath from n-doping (Supporting Information Figure S3). To define pn junctions in the NWs, we start by coating the NW arrays with PMMA and then use electron-beam lithography to pattern the PMMA blocking layer on top of the NWs. We p-dope the entire length of the NWs with oxygen and finally selectively n-dope the exposed side of the NWs in the arrays with excess lead. The patterning of the PMMA blocking layer by electron-beam lithography is aligned with the underlying electrodes to fabricate adjacent p-type and n-type FETs that share in common the middle electrode. This acts to tie the drain electrodes of the n-type and p-type FETs, constructing the integrated CMOS inverter (Figure 2A). Figure 2B shows an SEM image of a completed PbSe NW array CMOS inverter. We confirm that the FET on the right shows p-type characteristics and that on the left shows n-type characteristics (Supporting Information Figure S4).

The electrical characteristics of the NW CMOS inverter are measured using four probes: three contacts to the electrodes and one to the back gate. The n-type FET has its source electrode connected to the inverter's supply voltage ( $V_{DD}$ ). The common electrode that serves as the drain terminals of the n-type FET and p-type FET is connected to the inverter's output ( $V_{OUT}$ ). The source electrode of the p-type FET is connected to ground ( $V_{SS}$ ).

VOL. 9 • NO. 7 • 7536-7544 • 2015

7539

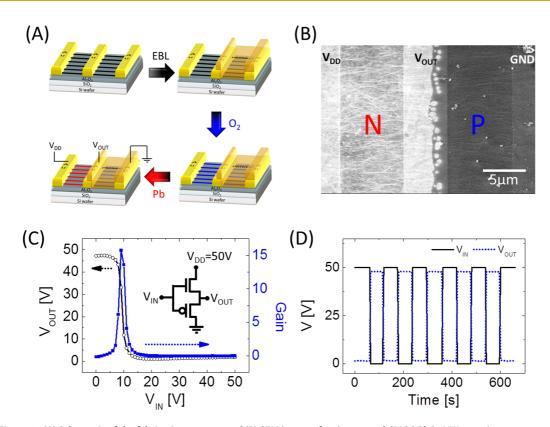

Figure 3. (A) SEM image and (inset) schematic of a PbSe NW array pn junction diode fabricated by p-doping through exposure to oxygen and n-doping through thermal evaporation of lead. (B) Dark current-voltage characteristics of the PbSe NW array pn junction diode. (C) Dynamic response of (left) the NW array pn junction photodiode in comparison to that for (right) a NW array p-type photoconductor. (D) Dynamic response (black) at  $V_{\rm G}$  = 0 V and (red)  $V_{\rm G}$  = 50 V and (E) transfer characteristics at  $V_{\rm DS} = 0$  V (black) before and (red) upon illumination of a gated PbSe NW array pn junction. The photoresponse in (C-E) is probed using ~1.2 mW/cm<sup>2</sup> 488 nm excitation. (F) Schematic of the energy band diagram of the gated PbSe NW photodiode (top) at  $V_{\rm G} = 0$  V and (bottom) at  $V_{\rm G} = 50$  V.

The common back gate of the FETs is connected to the inverter's input (V<sub>IN</sub>). Figure 2C (black curve) shows the voltage transfer characteristics of the fabricated NW CMOS inverter. At  $V_{IN} = 10$  V, the inverter operates as an amplifier with a gain  $(dV_{OUT}/dV_{IN})$  of approximately 15 (blue curve). At  $V_{IN}$  < 5 V or  $V_{IN}$  > 15 V, the inverter operates as a switch, inverting low  $V_{IN}$  to high  $V_{OUT}$  and high  $V_{\rm IN}$  to low  $V_{\rm OUT}$ .

Figure 2D shows the dynamic response of the NW CMOS inverter at  $V_{DD} = 50$  V to a square wave input signal  $V_{\rm IN}$  that switches from 0 to 50 V with a 200 s period and a 50% duty cycle. The output voltage  $V_{OUT}$  is a NOT logic function to the input signal V<sub>IN</sub>. The values of  $V_{\rm OUT}$  are measured to be  $\sim$ 48 and  $\sim$ 0.9 V for  $V_{\rm IN}$ at 0 and 50 V, respectively, utilizing  $\sim$ 94% of the 50 V

supply voltage. The nearly ideal switching behavior demonstrates the PbSe NW CMOS inverter function and its potential in electronic applications.

We further examine the possibility of adopting this technology to demonstrate optoelectronic devices. Using the processes described above, we fabricate PbSe NW array-gated pn junction diodes (Figure 3A). One signature of successful PbSe NW array pn junction formation is the rectifying behavior of the diode, seen in the dark current-voltage characteristics of the device (Figure 3B). The n-doping of the pn junction diodes may be carried out either through the solution-based PbCl<sub>2</sub> method or through thermal evaporation of elemental lead (Supporting Information Figure S5). The diode shows a rectification ratio of forward/reverse current

VOL.9 NO.7 7536-7544 2015

A

of ~60. While the pn junction shows rectifying behavior, the ideality factor is somewhat large at ~10 as we have not engineered the metal—semiconductor junction to form low resistance contacts and we expect partial Fermi level pinning.<sup>18</sup> Assuming an intrinsic carrier concentration of  $n_i = 4 \times 10^{14}$ /cm<sup>3</sup> from the ~0.45 eV band gap of the NWs<sup>18,19</sup> and acceptor ( $N_A$ ) and donor ( $N_D$ ) doping concentrations of 7  $\times 10^{17}$ /cm<sup>3</sup> (extracted from  $\Delta V_{TH}$  above) by 1 min exposure to oxygen for p-doping and by deposition of ~4 Å of lead for n-doping, we calculate a built-in potential

$$V_{\rm bi} = rac{k_{\rm B}T}{q} \ln{(rac{N_{\rm A}N_{\rm D}}{n_{\rm i}^2})} = \sim 0.38 \ {

m eV}$$

and a depletion width<sup>36</sup>

$$W = \sqrt{rac{2arepsilon_{

m s}arepsilon_{

m o}}{q}} rac{(N_{

m D}+N_{

m A})}{N_{

m D}N_{

m A}}V_{

m bi}} = \sim 200 \; {

m nm}$$

Here  $k_{\rm B}$  is Boltzmann's constant, *T* is temperature,  $\varepsilon_{\rm s}$  is the permittivity of ~200 for PbSe, and *q* is electrical charge.

We probe the switching response of the pn junction diode photocurrent to pulsed photoexcitation (Figure 3C, left). Photocurrent is generated upon illumination at  $V_{DS} = 0$  V, reflecting the formation of a pn junction and a built-in potential. No current is detected in the dark at  $V_{\rm DS}$  = 0 V, as it falls below the  $\sim$ 10 pA noise level of the instrument. The rise and fall times of our pn junction photodiode are less than the 1 s time resolution shown in Figure 3C (left) and are shorter than 10 ms time resolution of our instruments (Supporting Information Figure S6). For comparison, we fabricate a p-type PbSe NW array photoconductor by doping the whole length of the NWs with oxygen. The NW photoconductor has a switching time greater than a few seconds (Figure 3C, right). We emphasize that the photoresponse of our axially doped pn junction photodiode is >1000 times faster than that of a p-type photoconductor.<sup>36</sup> The responsivity of our photodiode is 0.14 A/W, which is comparable to that for the highest responsivity nanoscale semiconductor photodiodes,<sup>39</sup> which we expect may be increased by optimizing our device.

We further examine the properties of the NW array pn junctions in the dark and under illumination by gating the diodes in the FET platform. By applying a positive gate bias of  $V_G = 50$  V, the photocurrent at  $V_{DS} = 0$  V is enhanced by an order of magnitude compared to the device operated at  $V_G = 0$  V (Figure 3D). The increased photocurrent under the applied gate bias can be understood by comparing measurements of the FET transfer characteristics in the dark and under illumination, as shown in Figure 3E. As the gate bias is swept from negative to positive voltages, a current level is observed at positive voltage that is higher under illumination than in the dark. band diagram of the pn junction (Figure 3F) depicts the underlying physics. Depending on the amount of oxygen or lead introduced, the degree of p-doping and n-doping on either side of the junction can be controlled. For example, if we introduce more lead, we form a pn<sup>+</sup> diode, with a slightly greater majority carrier electron concentration on the n-side than the majority carrier hole concentration on the p-side of the junction. The asymmetric doping of the junction causes the depletion region to extend mostly into the more lightly p-doped side of the junction. The short depletion region limits the collection of photogenerated carriers and therefore the total photocurrent (highlighted by the green circle in Figure 3E and depicted in the corresponding band diagram on the top of Figure 3F). However, under the applied gate voltage, we can tune the carrier concentrations on either side of the junction and therefore tailor the width of the depletion region. As we apply an increasingly positive gate bias, the electron concentration on the n-side of the junction is accumulated and the hole concentration on the p-side of the junction is further depleted. The positive gate bias transforms the as-fabricated pn<sup>+</sup> junction into a  $p^{-}n^{++}$  junction. Since the width of the depletion region on the p-side increases more than the decrease in the depletion width on the n-side for the same gate bias, the total depletion width is extended and ultimately enhances the photocurrent (highlighted by the purple circle in Figure 3E and depicted in the corresponding band diagram on the bottom of Figure 3F). For example, a shorter 30 s exposure to oxygen shifts

A schematic of the gate dependence of the energy

the threshold voltage less than 10 V, creating a hole concentration on the p-side of  $\sim 5 \times 10^{17}$ /cm<sup>3</sup>, and 10 Å of deposited lead shifts the threshold voltage more than -50 V, creating an electron concentration on the n-side of  $\sim$ 5  $\times$  10<sup>18</sup>/cm<sup>3</sup>. For these doping levels, a junction depletion width of  $\sim$ 150 nm is formed. For the gated-diode structure, we can calculate the change in carrier density  $\Delta n = -\Delta p = (\varepsilon_0 \varepsilon_s E)/q$  induced electrostatically by the gate voltage ( $V_G = Ed$ ), where E is the electric field, d is the thickness, and  $\varepsilon_s$  is the relative permittivity of the dielectric stack.<sup>36</sup> If a positive gate bias of 50 V is applied to electrostatically modulate the carrier concentration through the 250 nm SiO<sub>2</sub> and 20 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric stack, the electron concentration increases and the hole concentration decreases by 4.6  $\times$  10<sup>17</sup>/cm<sup>3</sup>, assuming 10% coverage of NWs in the thin film. With the applied gate bias, the electron concentration on the n-side would be  $\sim$  5.5  $\times$  10<sup>18</sup>/cm<sup>3</sup> and the hole concentration on the p-side would be  $\sim$ 4  $\times$  10<sup>16</sup>/cm<sup>3</sup>. The 2 orders of magnitude drop in the hole concentration on the p-side of the junction would act to increase the depletion width to  $\sim$ 450 nm. The gated-diode structure allows us to electrostatically tune the carrier concentration and thereby optimize the NW pn junction photodiode performance.

VOL.9 NO.7 7536-7544 2015

(A)

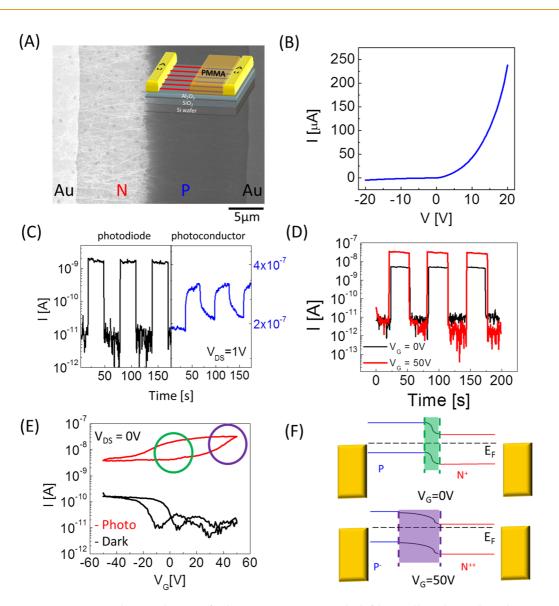

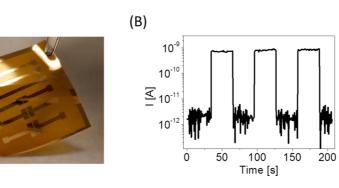

Figure 4. (A) Image of a PbSe NW array photodetector on a flexible Kapton substrate fabricated by p-doping through exposure to oxygen and n-doping through PbCl<sub>2</sub> treatment. (B) Dynamic response of a PbSe NW photodetector. The photoresponse in (B) is probed using  $\sim$ 1.2 mW/cm<sup>2</sup> 488 nm excitation.

We translate the assembly and selective doping used to fabricate PbSe NW array optoelectronic devices, described above on rigid silicon substrates, to flexible Kapton substrates. Figure 4A shows a photograph of a flexible PbSe NW array photodiode. We show that n-doping the NWs by both solution-based PbCl<sub>2</sub> treatment and thermal evaporation of elemental lead is compatible with pn junction fabrication on flexible plastics (Supporting Information Figure S5). The modulation between photocurrent and dark current is still approximately 400-600, comparable to that for the PbSe NW array photodiodes fabricated on rigid substrates (Figure 4B). While we use PMMA as a blocking layer to demonstrate the selective doping and construction of PbSe NW pn junctions, it has limited transmission beyond 2200 nm. For near- or mid-IR detectors, (1) the PMMA could be replaced by optically transparent photo- or e-beam resists, or (2) transparent dielectric materials (e.g., SiO<sub>2</sub>,

## and then the patterned dielectric material could be used as the blocking layer in the NW pn junction fabrication.

MgF<sub>2</sub>) could be deposited and the PMMA lifted off,

In conclusion, we demonstrate the selective n- and p-doping of colloidal PbSe NW arrays and exploit axial doping to create pn junction, PbSe NW arrays as the building blocks of integrated electronic circuitry and photodiode-based photodetectors. Scaling to shorter channel lengths and to single NW channel widths promises to optimize device performance for low-voltage, high-speed, and high-density circuits. Higher-performance photodiodes may be realized by scaling the channel length to reduce carrier diffusion through the quasi-neutral regions and by extending these methods for selective doping to construct PIN (p-type/intrinsic/n-type) junctions.

### **EXPERIMENTAL SECTION**

**Materials.** All manipulations were carried out using standard Schlenk line techniques under dry nitrogen. Tri-*n*-octylphosphine (further referred to as TOP, 90%), oleylamine (70%), oleic acid (OA, 90%), diphenyl ether (99%), lead chloride (PbCl<sub>2</sub>, 99%), amorphous selenium pellets (99.999%), MPTS (95%), anhydrous methanol, anhydrous isopropyl alcohol, anhydrous acetonitrile, anhydrous hexane, anhydrous chloroform, and anhydrous toluene were bought from Aldrich. Lead acetate trihydrate was purchased from Fisher Scientific Co., and *n*-tetradecylphosphonic acid (TDPA, 97%) was purchased from Strem.

Methods. PbSe NW Synthesis. Colloidal PbSe NWs are synthesized by a solution-based chemical method as previously reported.<sup>19,22</sup> First, 0.76 g of lead acetate trihydrate iss dissolved in 2 mL of oleic acid with 10 mL of diphenyl ether. This solution is heated at 150 °C for 30 min under a nitrogen flow to form a lead oleate complex. Subsequently, the solution is allowed to sit and cool to 60 °C. Four milliliters of 0.167 M trioctylphosphine selenide (TOPSe) is added gradually to the existing solution to prevent premature nucleation of PbSe nanostructures. This lead oleate/TOPSe solution is then quickly injected into a prepared solution of 0.2 g of TDPA dissolved in 15 mL of diphenyl ether at 250 °C. The temperature control during this injection step and the subsequent growth step is crucial to the formation of PbSe NWs with a straight morphology. After approximately 50 s of heating and fast stirring, the reaction mixture is cooled to room temperature by using a water bath. The resulting crude solution is then diluted with an equal amount of hexane and then centrifuged at 4000 rpm for 5 min. The precipitated NWs are redispersed in chloroform. Straight NWs with diameters of approximately 10 nm and lengths of >10  $\mu$ m are formed.

*PbSe NW Array FET Preparation.* FETs are fabricated on n-doped silicon wafers with 250 nm of thermally grown SiO<sub>2</sub> (Silicon Inc.). Al<sub>2</sub>O<sub>3</sub> (20 nm) is deposited as a part of the dielectric stack using atomic layer deposition. The added Al<sub>2</sub>O<sub>3</sub> further decreases the FET hysteresis. Photolithography and thermal evaporation of Au are used to define metal electrodes. Devices are thoroughly cleaned with isopropyl alcohol, acetone, and deionized water and by exposure to UV-ozone for 20 min. Devices are then placed in a 5% solution of MPTS in toluene overnight.<sup>21</sup>

The NW dispersion is further diluted in octane to a concentration of 100 g/mL, and several drops of a 10 wt % solution of HD-PVP copolymer in octane are added. The NWs are aligned by the electrophoresis method. The NW dispersion is dropcast onto the FET channel while applying a dc electric field of  $10^4 - 10^5$  V/cm for 10 - 20 s. The device channel dimensions are 20  $\mu$ m in length and 300  $\mu$ m in width. The devices are then washed with methanol and chloroform to remove impurities, excess organic compounds, and polymer. The samples are then immersed in a 10 mg/mL NH<sub>4</sub>SCN solution in methanol for 30 s and then thoroughly rinsed with methanol and chloroform to remove excess ligand.

PbSe NW Array pn Junction Preparation. After ligand exchange with thiocyanate, PMMA (from Microchem) 495A4 and

www.acsnano.org

950A4 electron-beam lithography resists are spin-cast at 3000 rpm for 1 min and baked at 180 °C for 3 min sequentially. Electron-beam lithography is used to open a window in the PMMA for selective doping of the exposed side of the NW arrays. After e-beam lithography and development, the device is then annealed at 180 °C for several seconds to get rid of some of the unwanted surface-bound oxygen that is introduced during electron-beam lithography in order to make the NW FETs ambipolar as a starting point. Then, the device is exposed to oxygen for approximately 1 min to p-dope the NWs. Excess Pb, approximately 4 Å, is then thermally evaporated onto the device to n-dope the exposed NWs in the window. It should be noted that PbCl<sub>2</sub> treatment can substitute for thermal evaporation to n-dope the NWs. To perform the PbCl<sub>2</sub> treatment, the device is immersed in a 10 mM PbCl<sub>2</sub> solution in oleylamine for 10 min at 80 °C and washed with hexanes several times.<sup>21</sup> Subsequently, additional PMMA layers are again spin-cast onto the device to minimize NW oxidation.

*PbSe NW Array CMOS Inverter.* The PbSe NW array CMOS inverter device is prepared following the method used for the PbSe NW array pn junction fabrication, with the addition of a third electrode as a bottom contact. A 4  $\mu$ m wide third electrode is introduced precisely at the center of the 20  $\mu$ m gap between the outer electrodes and therefore creates two 8  $\mu$ m channel length FETs, one that is p-type and the other is n-type.

*Characterization.* The devices are measured using an Agilent 4156C semiconductor parameter analyzer in combination with the Karl Suss PM5 probe station mounted in the nitrogen environment of a glovebox. Photoconductivity measurements are carried out by introducing 488 nm light from a Coherent Ar:Kr laser through a fiber-optic feedthrough into the glovebox. Photocurrents and dark currents are recorded by using an Agilent 4156C semiconductor parameter analyzer and a mechanical shutter.

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. The authors are grateful for primary support of this work from the NSF under Award DMR-1309053 for nanowire alignment, doping, device fabrication, and electronic and optoelectronic characterization. We thank the U.S. Department of Energy Office of Basic Energy Sciences, Division of Materials Science and Engineering, under Award DE-SC0002158 for nanowire synthesis.

Supporting Information Available: FTIR spectra of PbSe NWs before and after ligand exchange, output characteristics, and transfer characteristics of p-type and n-type PbSe NW FETs and their behavior with blocking layer, pn diode behavior of PbSe NW arrays on flexible substrates, and dynamic response of a gated PbSe NW array pn junction photodiode. The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsnano.5b02734.

#### **REFERENCES AND NOTES**

- Sargent, E. H. Colloidal Quantum Dot Solar Cells. Nat. Photonics 2012, 6, 133–135.

- Ip, A. H.; Thon, S. M.; Hoogland, S.; Voznyy, O.; Zhitomirsky, D.; Debnath, R.; Levina, L.; Rollny, L. R.; Carey, G. H.; Fischer, A.; et al. Hybrid Passivated Colloidal Quantum Dot Solids. *Nat. Nanotechnol.* **2012**, *7*, 577–582.

- Kovalenko, M. V.; Scheele, M.; Talapin, D. V. Colloidal Nanocrystals with Molecular Metal Chalcogenide Surface Ligands. *Science* 2009, *324*, 1417–1420.

- Talapin, D. V.; Murray, C. B. PbSe Nanocrystal Solids for n- and p-Channel Thin Film Field-Effect Transistors. *Science* 2005, 310, 86–89.

- 5. Kang, I.; Wise, F. W. Electronic Structure and Optical Properties of PbS and PbSe Quantum Dots. J. Opt. Soc. Am. **1997**, *14*, 1632.

- Semonin, O. E.; Luther, J. M.; Choi, S.; Chen, H.-Y.; Gao, J.; Nozik, A. J.; Beard, M. C. Peak External Photocurrent Quantum Efficiency Exceeding 100% *via* MEG in a Quantum Dot Solar Cell. *Science* **2011**, *334*, 1530–1533.

- Beard, M. C.; Midgett, A. G.; Law, M.; Semonin, O. E.; Ellingson, R. J.; Nozik, A. J. Variations in the Quantum Efficiency of Multiple Exciton Generation for a Series of Chemically Treated PbSe Nanocrystal Films. *Nano Lett.* 2009, *9*, 836–845.

- Sukhovatkin, V.; Hinds, S.; Brzozowski, L.; Sargent, E. Colloidal Quantum-Dot Photodetectors Exploiting Multiexciton Generation. *Science* 2009, *324*, 1542–1544.

- Oh, S.; Wang, Z.; Berry, N.; Choi, J. Engineering Charge Injection and Charge Transport for High Performance PbSe Nanocrystal Thin Film Devices and Circuits. *Nano Lett.* 2014, 14, 6210.

- Wang, X.; Koleilat, G.; Tang, J.; Liu, H. Tandem Colloidal Quantum Dot Solar Cells Employing a Graded Recombination Layer. *Nat. Photonics* 2011, *5*, 480–484.

- Konstantatos, G.; Sargent, E. H. Colloidal Quantum Dot Photodetectors. *Infrared Phys. Technol.* 2011, 54, 278–282.

- Bae, W. K.; Joo, J.; Padilha, L. A.; Won, J.; Lee, D. C.; Lin, Q.; Koh, W.; Luo, H.; Klimov, V. I.; Pietryga, J. M. Highly Effective Surface Passivation of PbSe Quantum Dots through Reaction with Molecular Chlorine. J. Am. Chem. Soc. 2012, 134, 20160–20168.

- Kim, D.; Choudhury, K.; Lee, J. PbSe Nanocrystal-Based Infrared-to-Visible Up-Conversion Device. *Nano Lett.* 2011, 11, 2109–2113.

- Liang, W.; Rabin, O.; Hochbaum, A. I.; Fardy, M.; Zhang, M.; Yang, P. Thermoelectric Properties of p-Type PbSe Nanowires. *Nano Res.* 2009, *2*, 394–399.

- Liang, W.; Hochbaum, A. I.; Fardy, M.; Rabin, O.; Zhang, M.; Yang, P. Field-Effect Modulation of Seebeck Coefficient in Single PbSe Nanowires. *Nano Lett.* **2009**, *9*, 1689–1693.

- 16. Rogalski, A. Infrared Detectors: Status and Trends. *Prog. Quantum Electron.* **2003**, *27*, 59–210.

- Rogalski, A.; Krzysztof, A.; Jaroslaw, R. Narrow-Gap Semiconductor Photodiodes; SPIE: Bellingham, WA, 2000.

- Oh, S. J.; Kim, D. K.; Kagan, C. R. Remote Doping and Schottky Barrier Formation in Strongly Quantum Confined Single PbSe Nanowire Field-Effect Transistors. ACS Nano 2012, 6, 4328–4334.

- Kim, D. K.; Vemulkar, T. R.; Oh, S. J.; Koh, W.-K.; Murray, C. B.; Kagan, C. R. Ambipolar and Unipolar PbSe Nanowire Field-Effect Transistors. ACS Nano 2011, 5, 3230–3236.

- Oh, S. J.; Berry, N. E.; Choi, J.-H.; Gaulding, E. A.; Paik, T.; Hong, S.-H.; Murray, C. B.; Kagan, C. R. Stoichiometric Control of Lead Chalcogenide Nanocrystal Solids To Enhance Their Electronic and Optoelectronic Device Performance. *ACS Nano* **2013**, *7*, 2413–2421.

- Oh, S. J.; Berry, N. E.; Choi, J.-H.; Gaulding, E. A.; Lin, H.; Paik, T.; Diroll, B. T.; Muramoto, S.; Murray, C. B.; Kagan, C. R. Designing High-Performance PbS and PbSe Nanocrystal Electronic Devices through Stepwise, Post-synthesis, Colloidal Atomic Layer Deposition. *Nano Lett.* **2014**, *14*, 1559–1566.

- Cho, K.-S.; Talapin, D. V.; Gaschler, W.; Murray, C. B. Designing PbSe Nanowires and Nanorings through Oriented Attachment of Nanoparticles. J. Am. Chem. Soc. 2005, 127, 7140–7147.

- Kim, D. K.; Lai, Y.; Vemulkar, T. R.; Kagan, C. R. Flexible, Low-Voltage, and Low-Hysteresis PbSe Nanowire Field-Effect Transistors. ACS Nano 2011, 5, 10074–10083.

- Talapin, D. V.; Black, C. T.; Kagan, C. R.; Shevchenko, E. V.; Afzali, A.; Murray, C. B. Alignment, Electronic Properties, Doping, and On-Chip Growth of Colloidal PbSe Nanowires. *J. Phys. Chem. C* 2007, *111*, 13244–13249.

- Fafarman, A.; Koh, W.; Diroll, B. Thiocyanate Capped Nanocrystal Colloids: A Vibrational Reporter of Surface Chemistry and a Solution-Based Route to Enhanced Coupling in Nanocrystal Solids. J. Am. Chem. Soc. 2011, 133, 15753–15761.

- Koh, W.; Saudari, S. R.; Fafarman, A. T.; Kagan, C. R.; Murray, C. B. Thiocyanate-Capped PbS Nanocubes: Ambipolar Transport Enables. *Nano Lett.* **2011**, *11*, 4764–4767.

- Choi, J.-H.; Fafarman, A. T.; Oh, S. J.; Ko, D.-K.; Kim, D. K.; Diroll, B. T.; Muramoto, S.; Gillen, J. G.; Murray, C. B.; Kagan, C. R. Bandlike Transport in Strongly Coupled and Doped

Quantum Dot Solids: A Route to High-Performance Thin-Film Electronics. *Nano Lett.* **2012**, *12*, 2631–2638.

- Choi, J.-H.; Oh, S. J.; Lai, Y.; Kim, D.; Zhao, T.; Fafarman, A. T.; Diroll, B. T.; Murray, C. B.; Kagan, C. R. *In Situ* Repair of High-Performance, Flexible Nanocrystal Electronics for Large-Area Fabrication and Operation in Air. *ACS Nano* 2013, *7*, 8275–8283.

- 29. Graham, R.; Yu, D. High Carrier Mobility in Single Ultrathin Colloidal Lead Selenide Nanowire Field Effect Transistors. *Nano Lett.* **2012**, *12*, 4360–4365.

- 30. Ravich, U. I. *Semiconducting lead chalcogenides*; Plenum Press: New York, 1970.

- Jones, R. H. The Reaction of Oxygen with Lead Selenide. Proc. Phys. Soc. London, Sect. B 1957, 70, 1025–1032.

- Leschkies, K. S.; Kang, M. S.; Aydil, E. S.; Norris, D. J. Influence of Atmospheric Gases on the Electrical Properties of PbSe Quantum-Dot Films. J. Phys. Chem. C 2010, 114, 9988– 9996.

- Wunnicke, O. Gate Capacitance of Back-Gated Nanowire Field-Effect Transistors. *Appl. Phys. Lett.* 2006, *89*, 083102.

- Kim, D. K.; Fafarman, A. T.; Diroll, B. T.; Chan, S. H.; Gordon, T. R.; Murray, C. B.; Kagan, C. R. Solution-Based Stoichiometric Control over Charge Transport in Nanocrystalline CdSe Devices. ACS Nano 2013, 7, 8760–8770.

- 35. Goldberger, J.; Sirbuly, D. ZnO Nanowire Transistors. *J. Phys. Chem. C* **2005**, *109*, 9–14.

- Sze, S. M.; Ng, K. K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons: Hoboken, NJ, 2007.

- Fan, Z.; Lu, J. G. Gate-Refreshable Nanowire Chemical Sensors. Appl. Phys. Lett. 2005, 86, 123510.

- Zan, H.; Kao, S. The Effects of Drain-Bias on the Threshold Voltage Instability in Organic TFTs. *IEEE Electron Device Lett.* 2008, 29, 20.

- Konstantatos, G.; Sargent, E. H. Nanostructured Materials for Photon Detection. Nat. Nanotechnol. 2010, 5, 391–400.